# **ESD in Automotive In-Vehicle Networks**

SE IEEE EMC Society

# **Nexperia's Contacts for ESD Protection**

Lukas Droemer

Product Manager for Automotive ESD Protection

Stresemannallee 101

22592 Hamburg

lukas.droemer@nexperia.com +49 151 61 88 47 52 Dr. Andreas Hardock

Applications Marketing Manager for ESD and EMC Stresemannallee 101

22592 Hamburg

andreas.hardock@nexperia.com +49 151 197 83 136

## Motivation

Datasheet Parameters and Selection Criteria for ESD Protection Devices

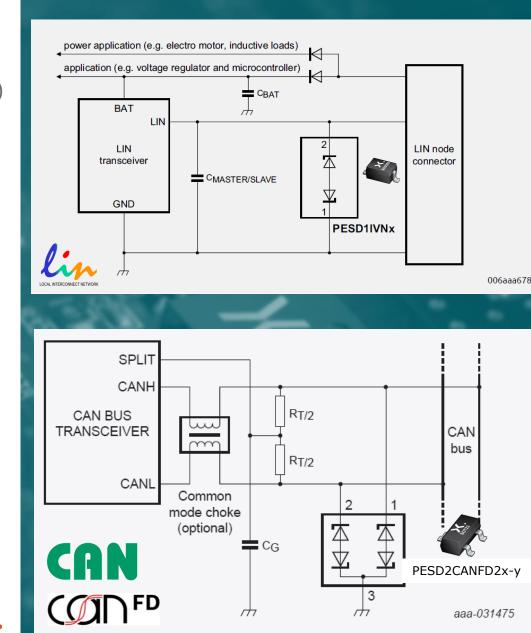

## ESD protection for

- Classics: LIN/CAN, CAN-FD

- Automotive Ethernet (OPEN Alliance)

- High Speed Links

## • Extra: How to simulate ESD?

# **ESD – Electro Static Discharge**

#### WHAT

A sudden electrostatic discharge between persons, devices or components

#### HOW

- A charged person touches an integrated circuit (IC)

- A charged IC drops on a grounded metal plate

- A charged machine touches an IC

- An electrostatic field is induced by high voltages

#### PROBLEM

- Causing malfunction (**reversible** by power-off-on cycle)

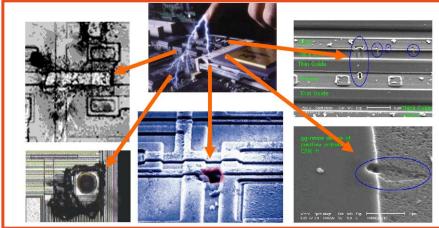

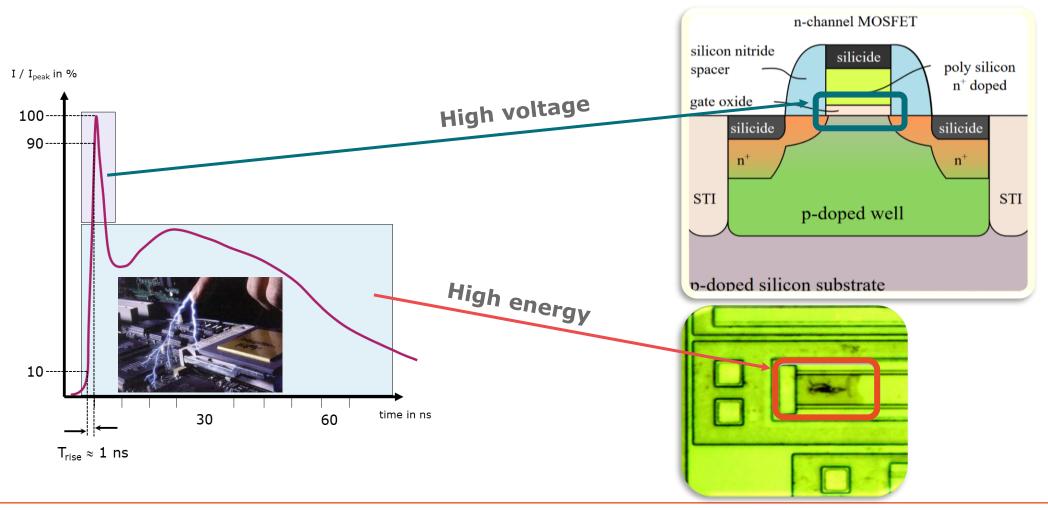

- Destruction of electrical components (irreversible): gate oxide, metallisation or PN junctions

# **ESD – Electro Static Discharge**

#### **Device level**

- ICs can be destroyed (ESD) during production (assembly, placement, handling)

- Qualification by standards (JEDEC)

- Human Body Model (HBM), 2kV for IC pins

- Machine Model (MM)

- Charged Device Model (CDM)

- ESD pulses are given to all IC pins.

- ESD "on-chip protection" protects against defects during production.

#### System level

- Complete Systems (e.g. clusters, head units) can be destroyed by ESD during operation or service

- "System Level" ESD standards

- IEC 61000-4-2

Electrostatic discharge immunity test

• ISO 10605

• ESD pulses are given to certain accessible interfaces.

Individual components (e.g. ICs) are not tested!

• Special ESD Devices are added on the board to avoid destruction by ESD.

public

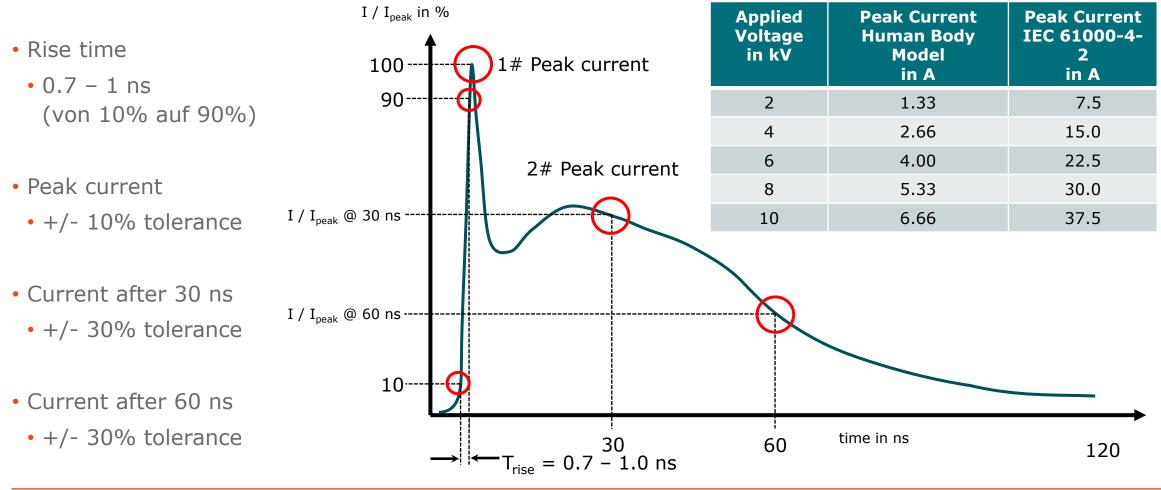

# ESD – System Level Testing: IEC 61000-4-2

Typical waveform of ESD current

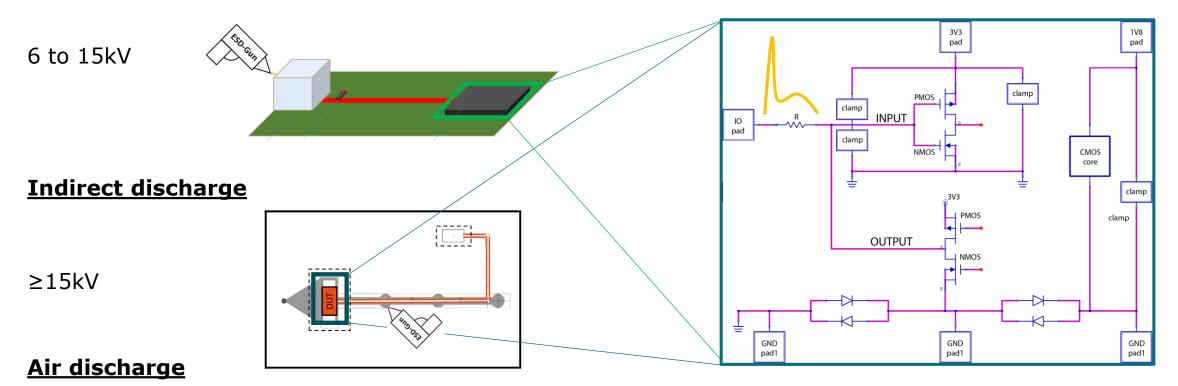

# **System ESD Testing**

#### **Direct (contact) discharge:**

## Strongly dependent on the system.

8 nexperia.com

## **ESD – Defects caused by ESD**

Destruction mechanism

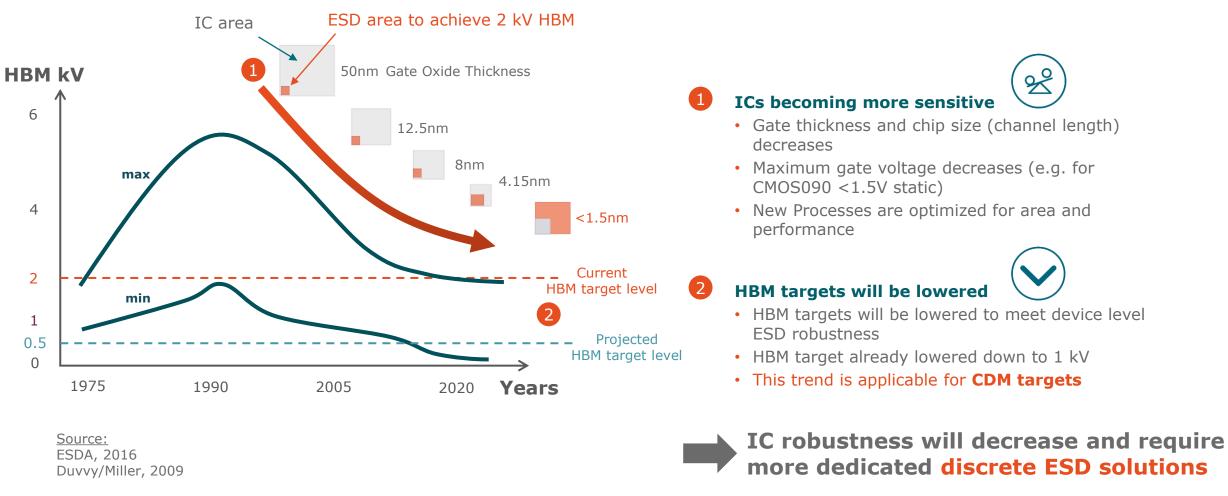

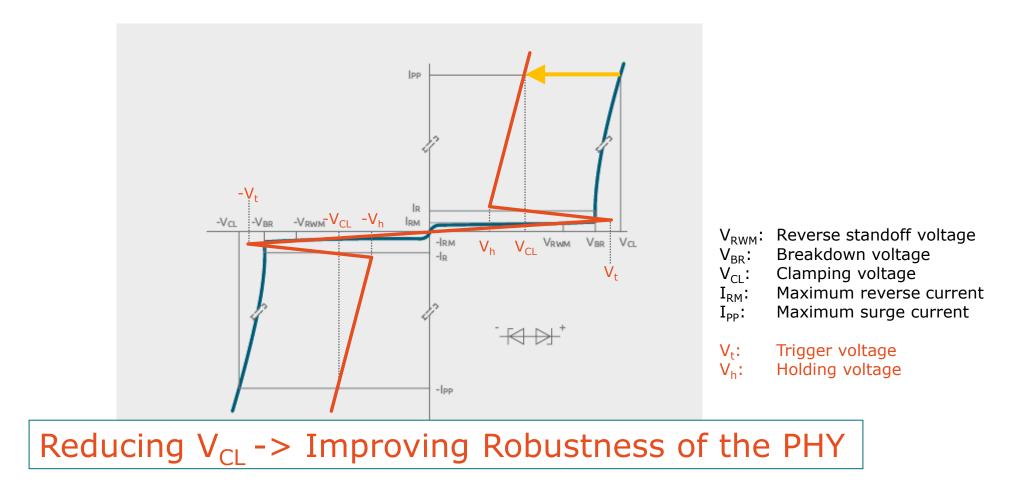

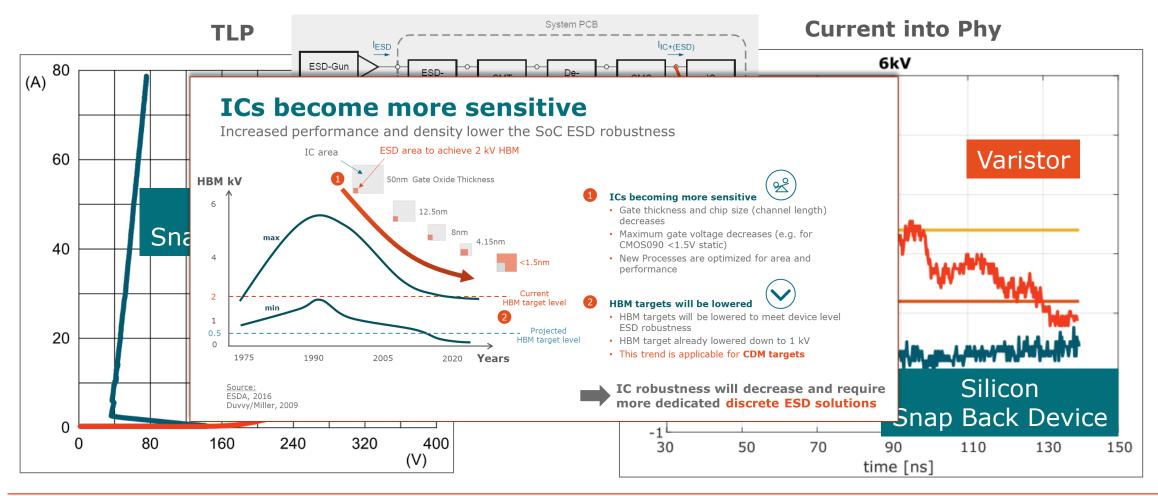

# **ICs become more sensitive**

Increased performance and density lower the SoC ESD robustness

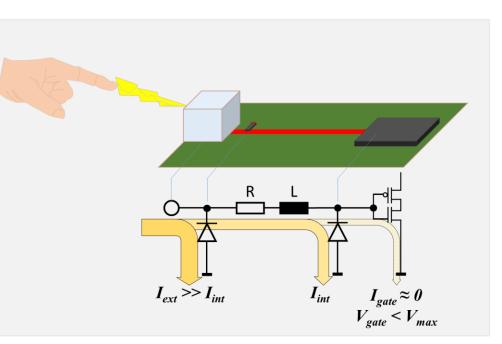

# **Benefits of external ESD protection**

Example CAN bus with PESD2IVN24-T

|                     | Device level       | System level                     |

|---------------------|--------------------|----------------------------------|

| IC/Transceiver      | ESD robustness w/o | ESD robustness with PESD2IVN24-T |

| TLE 9263BQXV33XUMA1 | + 8 kV (HBM)       | + 30 kV                          |

| TLE 9262BQXXUMA1    | + 8 kV (HBM)       | + 30 kV                          |

| MCP25625 E/SS       | + 8 kV (HBM)       | + 30 kV                          |

| LPC11C22FBD48/301   | + 8 kV (HBM)       | + 30 kV                          |

| SN65HVD232QDRQ1     | + 11 kV (HBM)      | + 30 kV                          |

| TLE7250GXUMA1       | + 10 kV (HBM)      | + 30 kV                          |

| TJA1042T/3,118      | + 12 kV (HBM)      | + 30 kV                          |

| TJA1044T            | + 10 kV (HBM)      | + 30 kV                          |

| :                   | :                  | +30 kV                           |

External ESD Protection can handle more ESD current and can be chosen application specific.

Very Robust System in the Field!

# **Selection Criterion**

Package (shape/size/footprint)

Side-wettable flanks for AOI

Number of signal lines

e.g. differential or single ended, one or more channels

Electrical performance

- Reverse stand-off voltage  $V_{RWM}$

- Breakdown or trigger voltage  $V_{\rm br}$  or  $V_{\rm t}$

- Clamping voltage V<sub>clamp</sub>

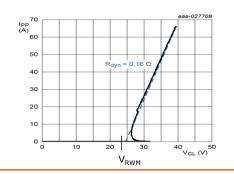

- Dynamic resistance R<sub>dyn</sub>

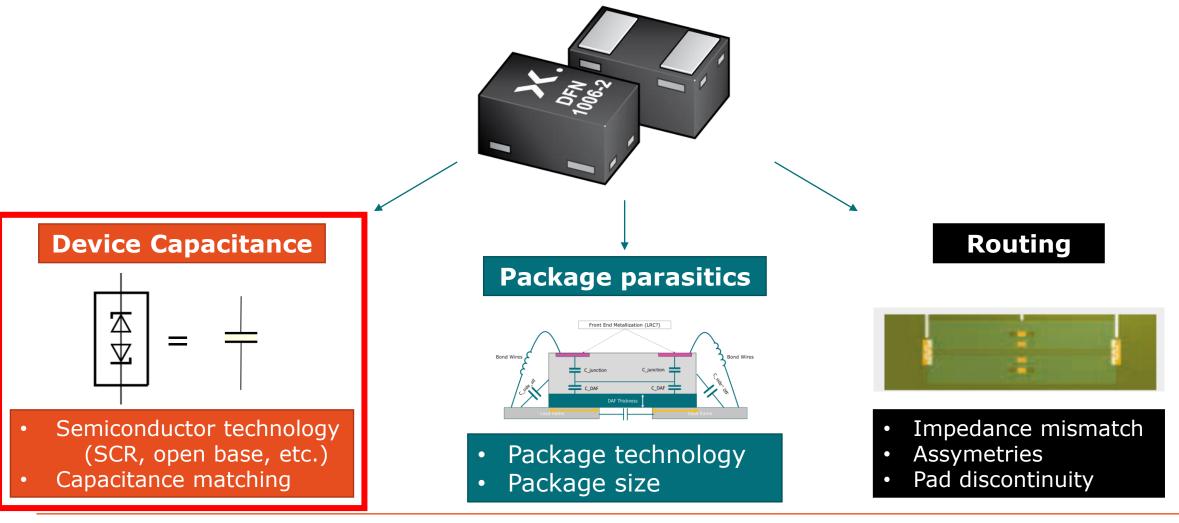

- **Device capacitance C**<sub>d</sub> and other parasitics

DEN1006BE

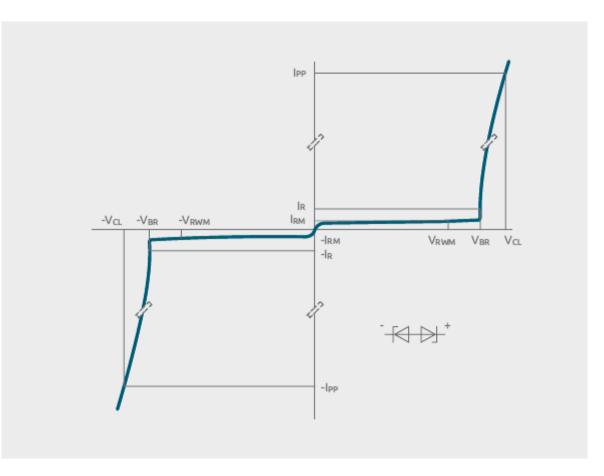

## **Characteristics of ESD Protections**

Classical Zener Characteristic

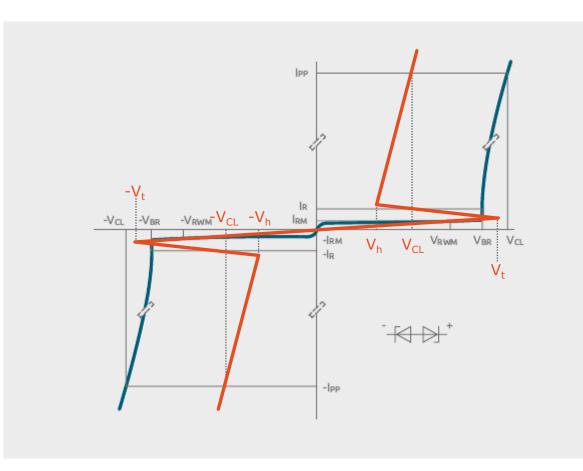

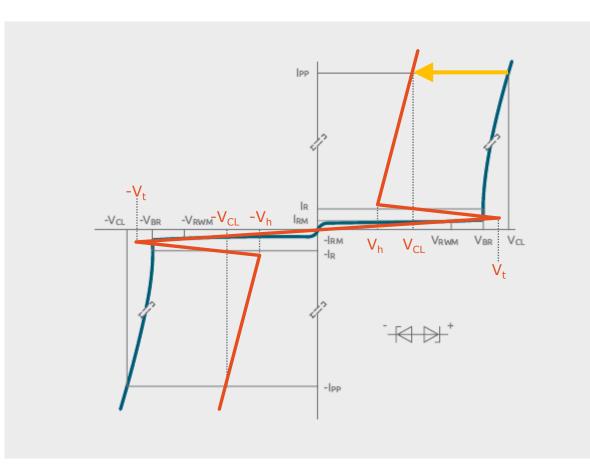

## **Characteristics of new ESD Protections**

Snap Back

Reverse standoff voltage V<sub>RWM</sub>: V<sub>BR</sub>: Breakdown voltage V<sub>CL</sub>: Clamping voltage Maximum reverse current I<sub>RM</sub>: I<sub>PP</sub>: Maximum surge current

Trigger voltage V<sub>h</sub>: Holding voltage

V<sub>t</sub>:

## **Characteristics of new ESD Protections**

Snap Back

Reverse standoff voltage V<sub>RWM</sub>: V<sub>BR</sub>: Breakdown voltage V<sub>CL</sub>: Clamping voltage Maximum reverse current I<sub>RM</sub>: I<sub>PP</sub>: Maximum surge current

Trigger voltage V<sub>h</sub>: Holding voltage

V<sub>t</sub>:

# **Characteristics of new ESD Protections**

Snap Back

# **Example: Automotive Ethernet**

Clamping performance and system robustness

## **Automotive ESD Protection**

## LIN/CAN

- Requirement for ESD protection depend on OEM (approval list)

- ->Emission and Immunity: DPI, Pulses, ESD (in combination with transceiver!)

- Common requirements:

|                  | LIN                   | CAN HS | CAN FD                  |

|------------------|-----------------------|--------|-------------------------|

| Cd               | 30 100pF              | 10 30p | F 3.5 10 (30) pF        |

| $\Delta Cd/Cd$   | nA typical <          |        | 0.5% for modern devices |

| N/               | 12 V Board            | d Net  | 24 V Board Net          |

| V <sub>RWM</sub> | >24V ISO16750-2 (28V) |        | >32V ISO16750-2         |

X

## **Automotive ESD Protection**

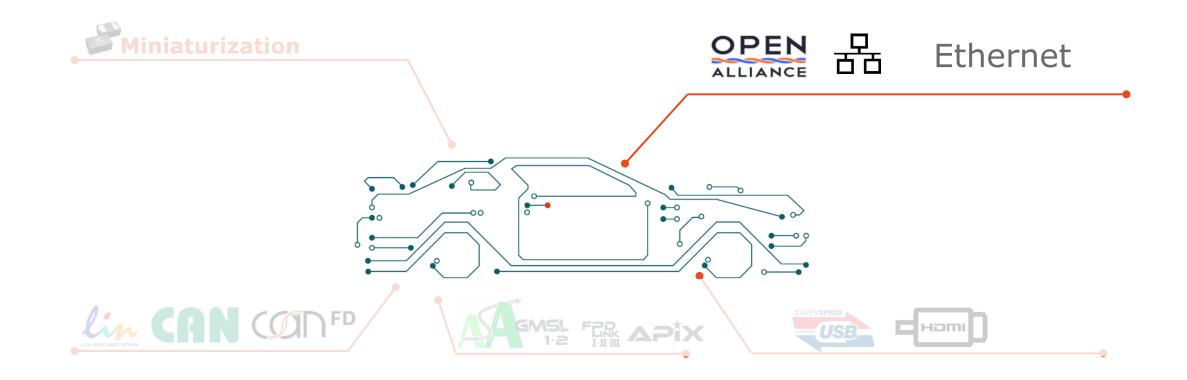

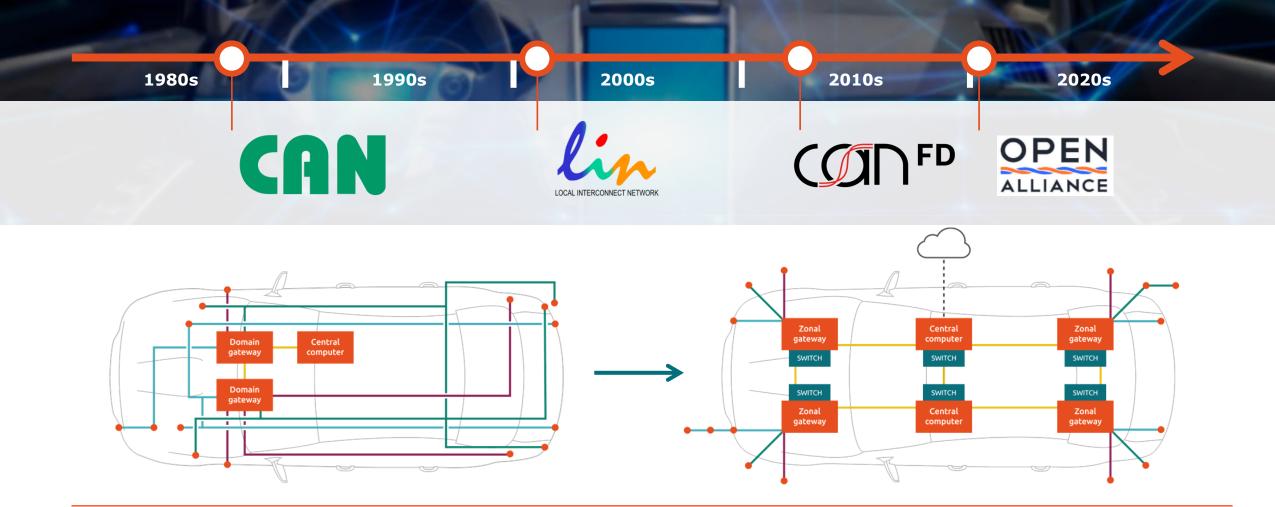

## **Evolution of In-Vehicle Networking**

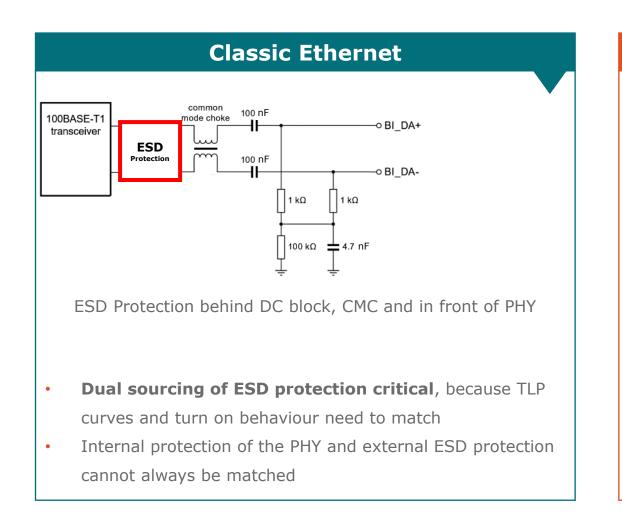

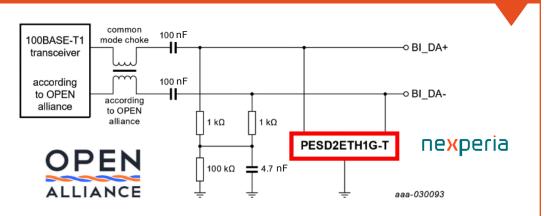

## **Classic Ethernet vs. OPEN Alliance**

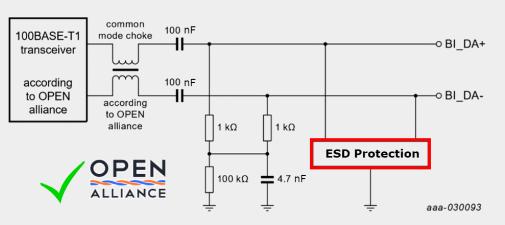

#### **OPEN Alliance Ethernet**

ESD Protection in front of DC Block, CMC and PHY

Dual sourcing of ESD protection uncritical, because ESD

protection in front of DC block and CMC protect whole system

External ESD protection is decoupled from internal protection of

the PHY. PESD2ETH1G-T matches with every PHY

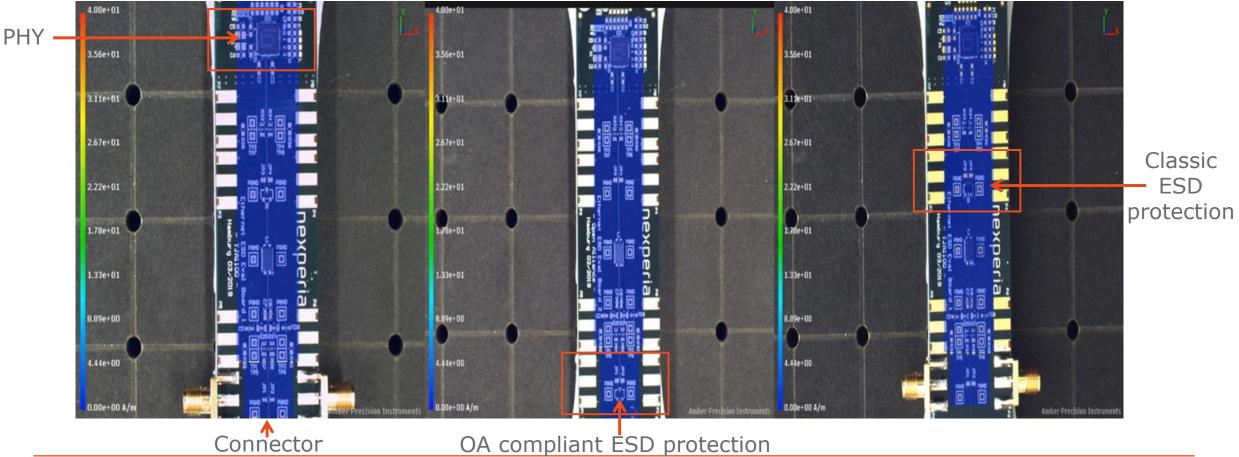

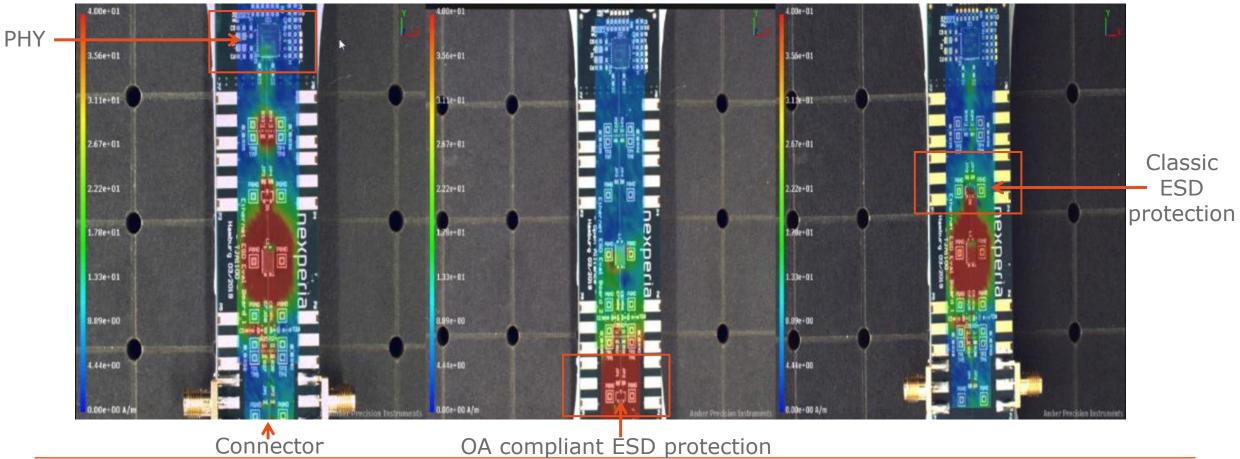

# **100BASE-T1 concept comparison**

Comparison of ESD protection concepts evaluated by EMI scanner

**No Protection**

OPEN

ALLIANCE

**Classic Protection**

# **100BASE-T1 concept comparison**

Comparison of ESD protection concepts evaluated by EMI scanner OPEN

**No Protection**

ALLIANCE

**Classic Protection**

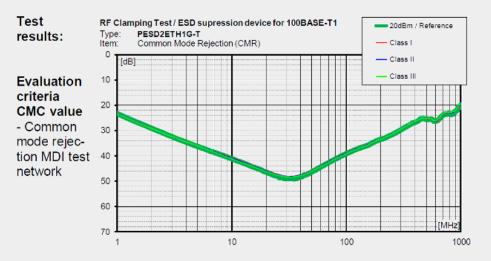

# **OPEN Alliance Spec. for ESD protection devices**

General requirements

### General requirements

- Bi-direction device, 15kV IEC, 1000 discharges

- Trigger voltage > 100V, V<sub>DC,max</sub> > 24V

#### Additional tests

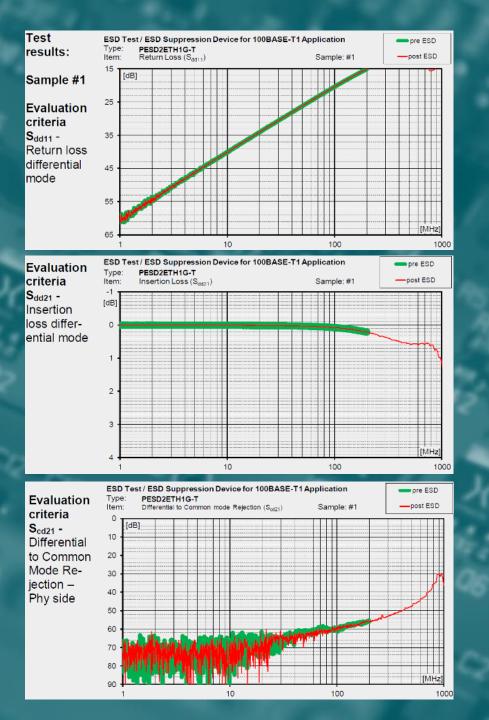

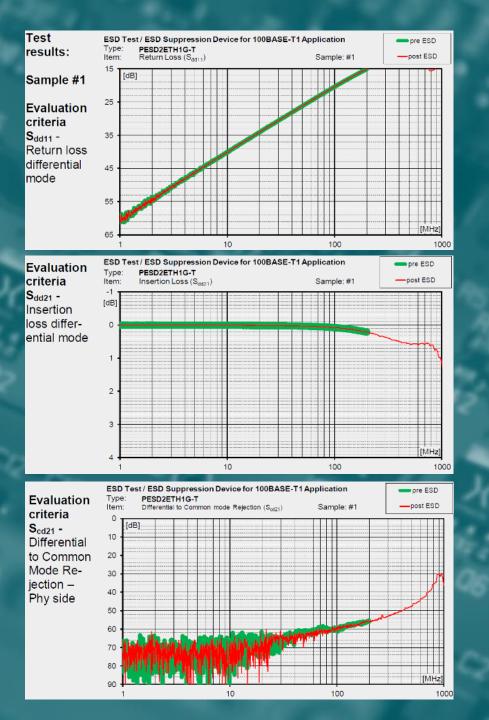

## Signal Integrity

- Mixed mode S-parameter measurements

- To evaluate transmission, symmetry, and mode conversion, replaces requirements on  $C_{\rm p}$  and matching

- Damage from ESD

- To verify degradation, first measure S-parameters, apply ESD (8kV) discharges, and check S-parameters again

#### • ESD discharge current measurement

- Quantification of the current that would flow into the PHY

- Unwanted clamping

## Immunity

ESD, PHY

Evaluate impact of ESD device onto RF immunity testing

## **OPEN Alliance Spec. for ESD protection devices**

Damage from ESD

- General requirements

- Bi-direction device, 15kV IEC, 1000 discharges

- Trigger voltage > 100V,  $V_{DC,max}$  > 24V

#### Additional tests

- Mixed mode S-parameter measurements

- To evaluate transmission, symmetry, and mode conversion, replaces requirements on  $C_{\rm p}$  and matching

## Damage from ESD

- To verify degradation, first measure S-parameters, apply ESD (8kV) discharges, and check S-parameters again

- ESD discharge current measurement

- Quantification of the current that would flow into the PHY

- Unwanted clamping

- Evaluate impact of ESD device onto RF immunity testing

## **OPEN Alliance Spec. for ESD protection devices**

Damage from ESD

- General requirements

- Bi-direction device, 15kV IEC, 1000 discharges

- Trigger voltage > 100V,  $V_{DC,max}$  > 24V

#### Additional tests

- Mixed mode S-parameter measurements

- To evaluate transmission, symmetry, and mode conversion, replaces requirements on  $C_{\rm p}$  and matching

## Damage from ESD

- To verify degradation, first measure S-parameters, apply ESD (8kV) discharges, and check S-parameters again

- ESD discharge current measurement

- Quantification of the current that would flow into the PHY

- Unwanted clamping

- Evaluate impact of ESD device onto RF immunity testing

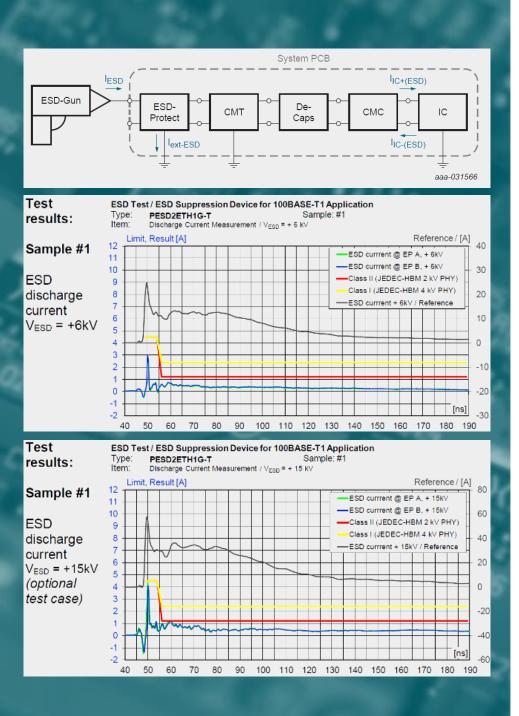

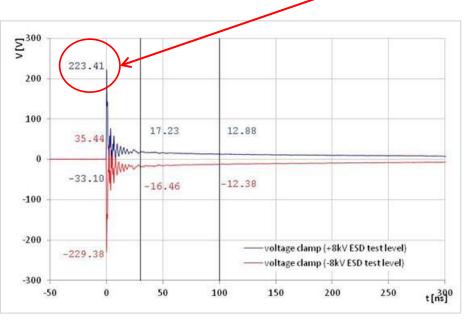

# **OPEN Alliance Spec. for ESD protection devices**

ESD discharge current measurement

- General requirements

- Bi-direction device, 15kV IEC, 1000 discharges

- Trigger voltage > 100V,  $V_{DC,max}$  > 24V

## Additional tests

- Mixed mode S-parameter measurements

- To evaluate transmission, symmetry, and mode conversion, replaces requirements on  $C_{\rm p}$  and matching

- Damage from ESD

- To verify degradation, first measure S-parameters, apply ESD (8kV) discharges, and check S-parameters again

## • ESD discharge current measurement

- Quantification of the current that would flow into the PHY

- Unwanted clamping

- Evaluate impact of ESD device onto RF immunity testing

## **OPEN Alliance Spec. for ESD protection devices**

Unwanted clamping

- General requirements

- Bi-direction device, 15kV IEC, 1000 discharges

- Trigger voltage > 100V,  $V_{DC,max}$  > 24V

## Additional tests

- Mixed mode S-parameter measurements

- To evaluate transmission, symmetry, and mode conversion, replaces requirements on  $C_{\rm p}$  and matching

- Damage from ESD

- To verify degradation, first measure S-parameters, apply ESD (8kV) discharges, and check S-parameters again

- ESD discharge current measurement

- Quantification of the current that would flow into the PHY

- Unwanted clamping

- Evaluate impact of ESD device onto RF immunity testing

## **Automotive ESD Protection**

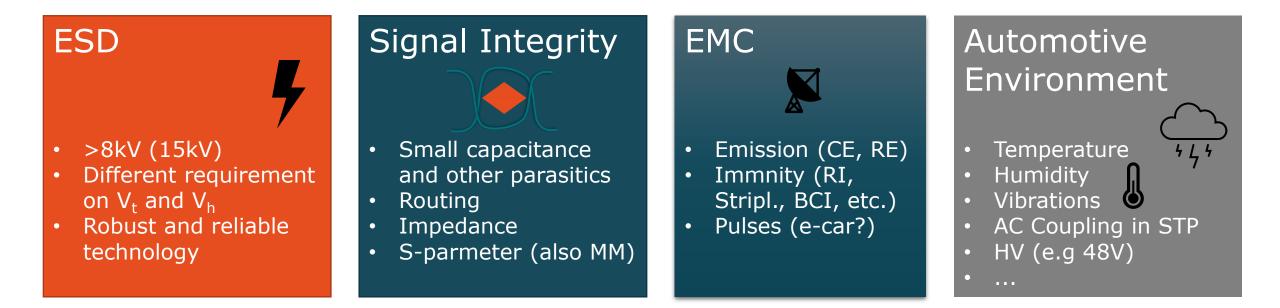

# **Challenges for High-Speed Interfaces**

## Semiconductor technology, HF analysis (S-Param, Eye Diagramm, TDR), ESD Simulation - SEED, High-Speed Packages

31 nexperia.com

## **Parameters impacting Signal Integrity**

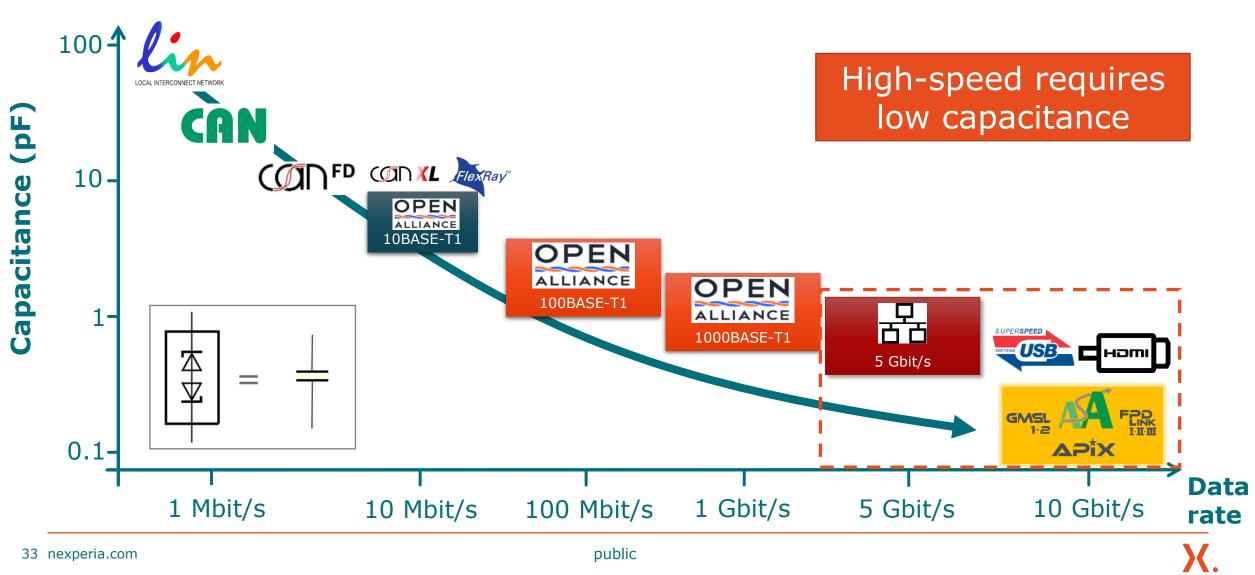

## **Application overview: capacitance vs. datarate**

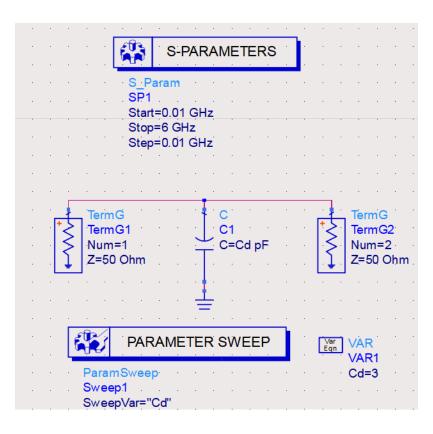

# **Impact of Capacitance**

S-Parameters

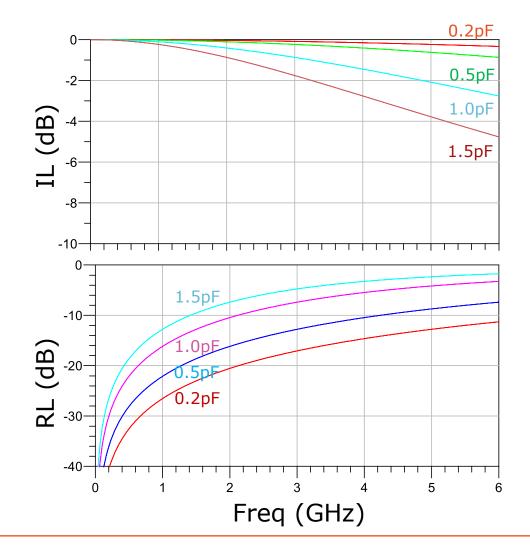

# **ESD Protection Device**

Measurement vs simulation of capacitor

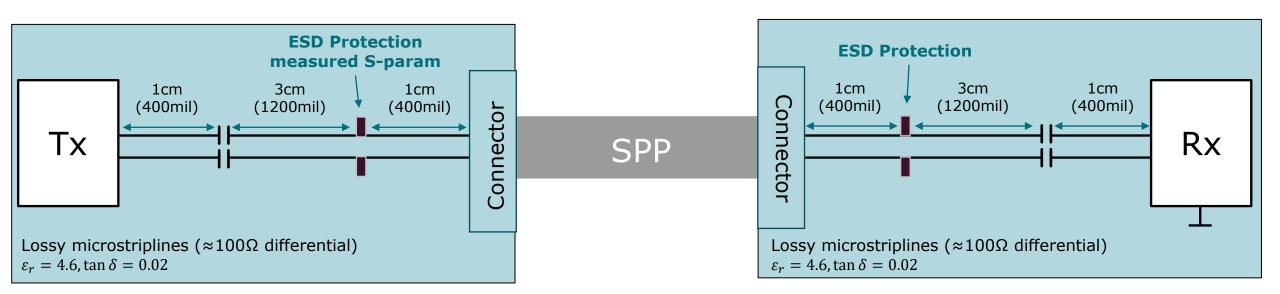

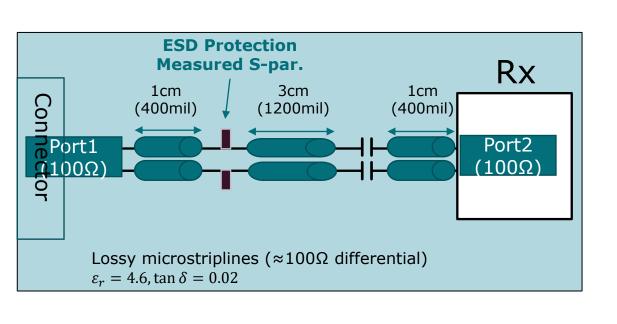

# **Simulation of a High Speed Link**

PHY – Cable - PHY

Simulate Rx/Tx system separately

Include cable

Include connector

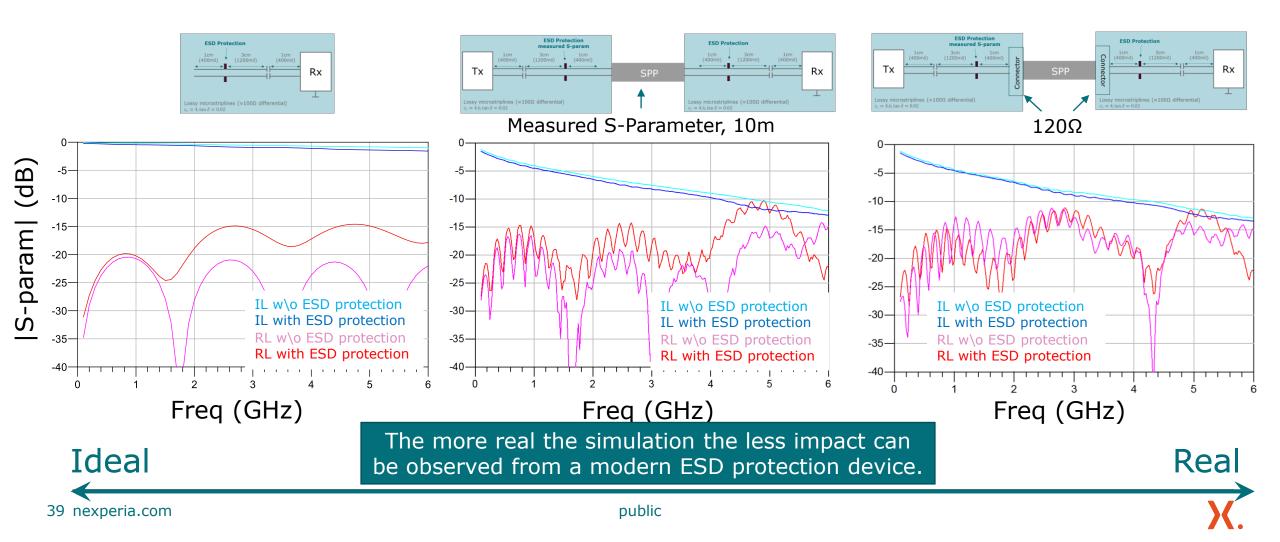

# **Simulation of High Speed Links**

S-parameters simulation in ADS

Ideal system, not including e.g. cable and connector!

38 nexperia.com

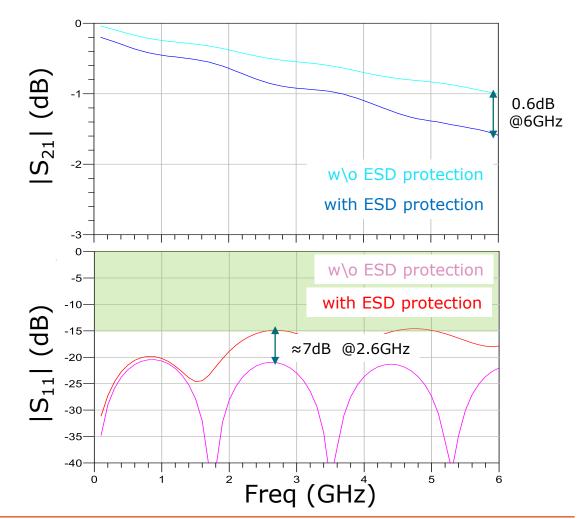

# **Simulation of a High Speed Link**

PHY – Cable – PHY: Results

# **Signal Integrity**

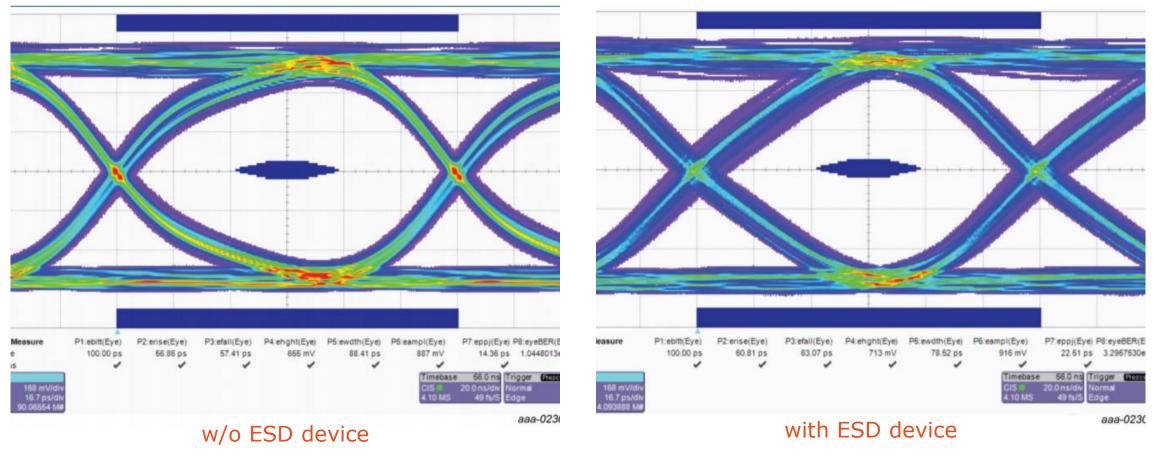

Eye Diagramm (Cd=0.17pF)

# **Package Aspects**

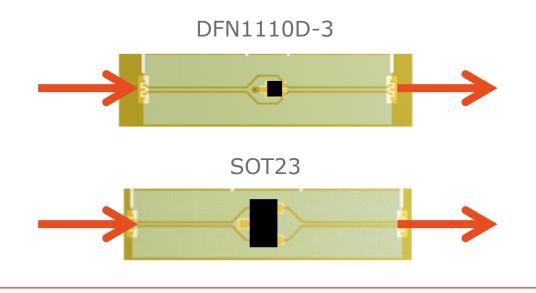

Comparison of SOT23 and DFN1110D-3 with PESD2CANFD24Vx ( $C_d = 5.2 \text{ pF}$ )

- Ca. 2 cm traces on FR4

- Dashed line: no footprint

- Clear advantage of leadless package

## Package aspects – Clamping behavior

For high-speed busses

- Rdyn governs the clamping voltage in a quasi-static condition

- The dynamic behavior is determined by inductances and turn-on behavior

Х

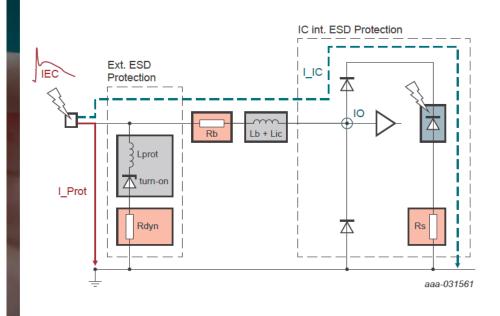

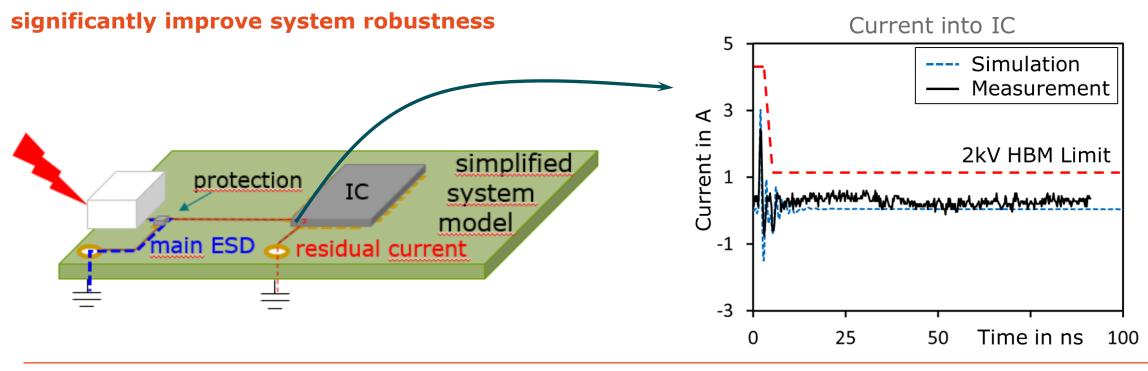

## System Efficient ESD Design (SEED)

- SEED simulates residual currents and voltages at IC pins

- Dynamic models for ESD protection and common mode chokes for ADS and Spice

- Allows to pick best protection during system concept design and

# Conclusion

- ESD can irreversibly distruct any electonic system, especially sensitive in-vehicle networks

- External ESD Protection can increase the system robustness of your system significantly

- ESD protection devices must be chosen for each application specifically

- Dedicated ESD protection can improve the system robustness of High-Speed applications without compromizing SI

- SEED simulations help to simplify the selection and design process

## **Service & Support**

Find out more about Nexperia and our products & services

## EFFICIENCY WINS.